## Overview

Stress engineering is mandatory to meet the performance targets of leading-edge CMOS technology and is now extending to strained SiGe channels and hybrid orientation of NMOS and PMOS devices. This involves a large number of possible device configurations for exploring and optimizing MOSFET performance, which can only be investigated efficiently with the help of TCAD. Yet, the complexity of stress effects, ranging from the impact of stress on process simulation to 3D effects and drain current enhancement in the quasi-ballistic transport regime of nanoscale transistors, makes TCAD simulation a challenging task.

Synopsys TCAD Services offers a range of services to address device optimization and process inre on engineering offer many degrees of freedom to optimize device

\_ðRð

DZBVőa`T\VedköR\_UdjRj`feðaciZ^Zf\_`ceY`U`iðTgideR]]`XcRaYZTð cZV\_eReZ\_dkr

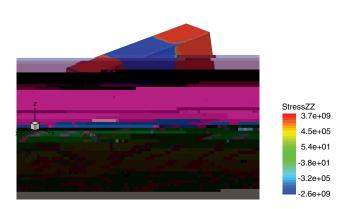

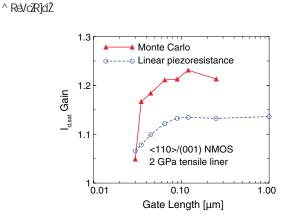

a VcWc^ R\_TVôn ZeYZ\_0eYVôXZgV\_0UVgZTVôn Z\_U` h ŽŒ 4 2 5 ôR]]` h dô WcôR\_0VWMTZV\_e6RddVdd^ V\_e6 WoeYVôUZWWcV\_e6T` \_WXKfcReZ \_dkûRdô Z]f decReVU0Z\_07ZKfcVô\*kôn YZTYôdY` h dôRôdj a ZTR]O\$ 5 ô` VTYR\_ZTR]ô decVddôdZ^ f]ReZ\_kôR\_U0Z\_07ZKfcVô\*kôn YVcVôeYVôVWWTe6 WXYZKYô decVddôrR\_UôbfRdZSR]]ZdeZTôecR\_da` ceô \_0eYVôUkdReôXRZ\_0Zdô UV^` \_decReVUŽ64 fccV\_e6decVddôV\_XZ\_VVcZ\_XôRaac` RTYVdôcV]j ô \_ôRô ]RcXVô\_f^ SVcô WodecVddôbVTY\_ZbfVd-eVeTYôde` a ðRj^` ` e b` h

Figure 1: Stress component normal to the gate interface in the Si body of the MOSFET.

Figure 2: Scaling of the stress-induced on-current gain.